CPU Time

什麼是電腦最基本的執行單位?

電腦裡面最核心的部分就是processor 處理器 而處理器的工作完完全全是依據使用者給它的命令 再依照這些命令來產生對應的行為 而這些命令我們叫做 instruction 指令

什麼是電腦最基本的時間單位?

我們知道電腦本身是一個sequential circuit 循序電路 而讓sequential circuit能夠正常順利的運作 最關鍵的就是需要有一個clock 去控制資料的同步以及更新 也因此電腦最基本的時間單位就是 clock cycle

CPU Time = CPU Clock Cycles * Clock Cycle Time = CPU Clock Cycles / Clock Rate

說明:

CPU time 可以視為是一個程式在CPU裡面執行了多少個 clock cycle 再乘上每一個clock cycle它實際花了多少的時間

而在這邊clock cycle其實就是一個週期 又因為我們知道週期跟頻率其實互為倒數的關係 所以CPU time也可以定義為: CPU的clock cycles 除以 clock rate (CPU的頻率)

這裡的clock rate 其實就是CPU的頻率 clock frequency

如果我們希望能夠提升系統的效能也就是減少CPU time?

方法一:

減少它的clock cycles

方法二:

提高這個處理器這個processor的 clock frequency, clock rate

實際上我們經常需要在一個處理器的頻率以及實際上它執行的指令的個數之間做折衷

而不太可能能夠同時得到一個頻率又快但是執行的cycle count又非常少的情形發生

最基本的指令需要幾個時間單位的執行時間呢?

Ans :不一定

思考一 :

舉個例子

如果乘法跟加法這兩個指令來相比

乘法需要花比較多的時間才能完成

因為乘法本身的複雜度是遠比加法來得高的

從這樣子的一個角度出發的話

其實每一個指令它所需要花的執行時間應該是不盡相同的

思考二 :

另一方面如果我們從處理器的設計技術

比如說single cycle, multi cycle或者pipeline

採用這些不同的設計技術

每一個基本指令所需要的執行時間

時間單位都可能不盡相同

而關於這方面的知識將會在Lecture 4的時候一併討論

每一個指令在CPU裡面執行的時候所需要的clock cycles

它的時間可能是不盡相同的

也因此如果我們想要了解一個程式在CPU裡面執行經過了多少個clock cycles

可以把它展開成為一個程式裡面有多少個指令乘上每一個指令需要執行多少個cycle

CPI = cycles per instruction

影響instruction count最重要的關鍵

- 在於這個程式本身它的特性是什麼

它的迴圈多不多?

它所經過的指令多不多?

以及這個指令集的特性?

- 當然還有更重要的就是compiler

因為它會把高階的程式語言

例如是C把它轉換成為 assembly language

- example

假設今天在一個處理器裡面

每一個指令所需要執行的cycle是不盡相同的

這個時候我們會用一個 "average 平均的CPI" 來代表整體的執行cycle

而這個東西平均的CPI會跟 "硬體的個性" 有關

當然它同時也是跟實際上 "這個程式的執行" 有關

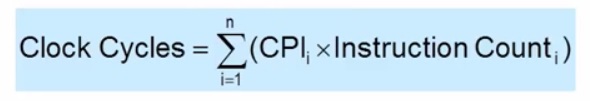

CPI in More Detail 平均CPI

每一個程式在處理器執行的時候所需要的clock cycle的個數

其實就會跟不同類型的指令 以及這個指令所對應到的CPI (cycle per instruction)有關

我們把指令的個數乘上它的CPI 把它給加總起來

就會是這個程式在這個處理器裡面執行

總共的clock cycle個數

平均的CPI

就是上面這邊剛才所推導的式子 把它除以全部這個程式裡面到底有多少個指令

有一點點像是加權的效果

總結 :

CPU time計算方法 :

一個程式裡面有多少個指令

而每一個指令它需要多少個clock cycle來執行

以及每一個cycle它到底花了多少的時間

把這些東西相乘起來就是一個程式在CPU裡面執行所花的時間。

因此如果希望提升電腦的效能提升CPU的效能就應該要從這些地方來著手。

X 表示有相關

解釋 :

- Instruction Set指令集特性 ...... RISC vs. SISC

如果我的指令集是比較複雜的 (一個指令它可以做很多件事情)

這一類型的指令我們通常把它叫做CISC (Complex instruction set computer)

相對於一個比較精簡的指令RISC (Reduced instruction set computer)

CISC它所需要花的instruction count的個數

可能會比RISC來得少

不太可能又要馬兒跑又要馬兒不吃草

所以如果我們花的指令的個數是少的

很可能每一個指令它所需要執行的時間就會比較長

- Organization處理器本身的架構

single cycle

multi cycle

pipeline

也會對於CPI造成影響

而對應的 它的clock的頻率 clock rate, clock frequency

也會有相同的影響

- Technology

半導體的技術

也會決定今天 IC 到底它可以跑的速度有多快